2021. 11. 17. 17:36ㆍ코딩/FPGA

블록 디자인을 만든 다음에

MicroBlaze를 불러온다

불러온 MB우클릭 또는 상단 녹색바의 Run Block Automation을 누른다

나는 아직 배우는 입장이라 용량을 넉넉 하게 128KB로 잡고 인터럽트는 사용을 안할것이기 때문에 체크박스는

가만히 둔채로 OK 버튼을 누른다

OK를 누르면 이러한 블록들이 나타날 것이다 이때 CLK을 더블클릭한다

sysclk 를 사용할것이기 때문에 커스텀 에서 sys clock로 바꿔준다.

GPIO, uart도 사용할 것이기 때문에 추가를 한다.

추가를 한뒤 상단의 Run Connection Automation을 선택한다

그러면 연결이 가능한 리스트가 뜨는데

그 리스트 들의 체크박스를 전부 체크한뒤에 ok를 누른다

연결이 다 됬으면 Create HDL Wrapper 를 누른다

생성된 탑에 맞춰서 XDC파일을 제작해주고

bitstream을 실행한다

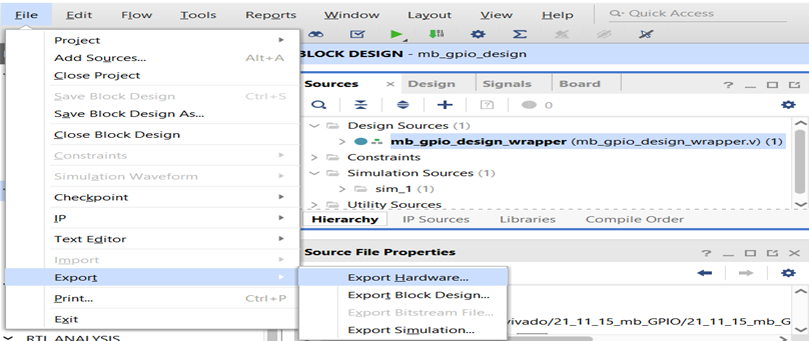

비트 스트림 이후 Export -> Export Hardware를 누른다

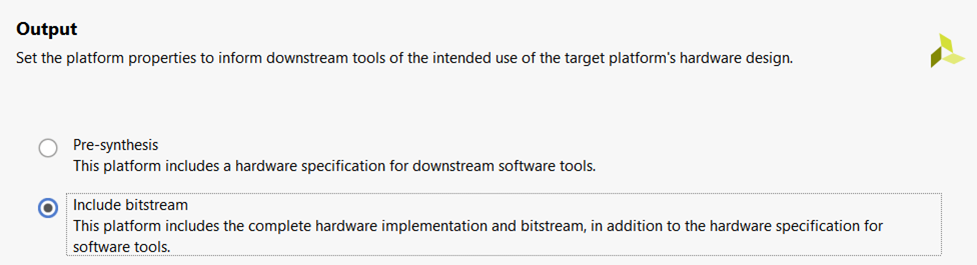

Include bitstream 을 선택하고

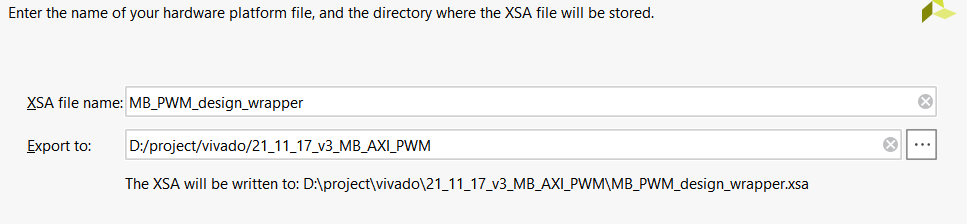

next를 누르면 저장경로 설정창이 뜬다

이때 저장하는 파일을 사용할 것이기 때문에 저장되는 경로를 확실히 알아두자.

저장을 했으면

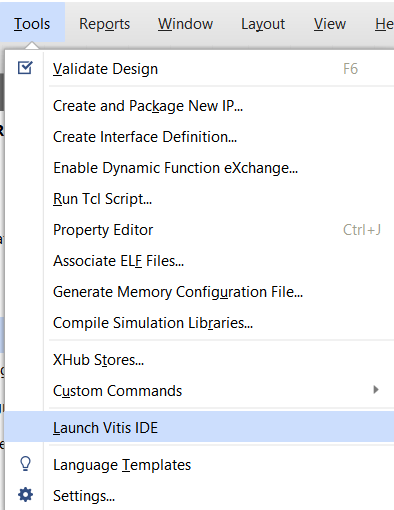

Tools 에서 Launch Vitis IDE를 선택한다

그러면 저장 경로를 정한뒤에

VITIS IDE 창이 뜨는데

여기서 Create Application Project를 누른다

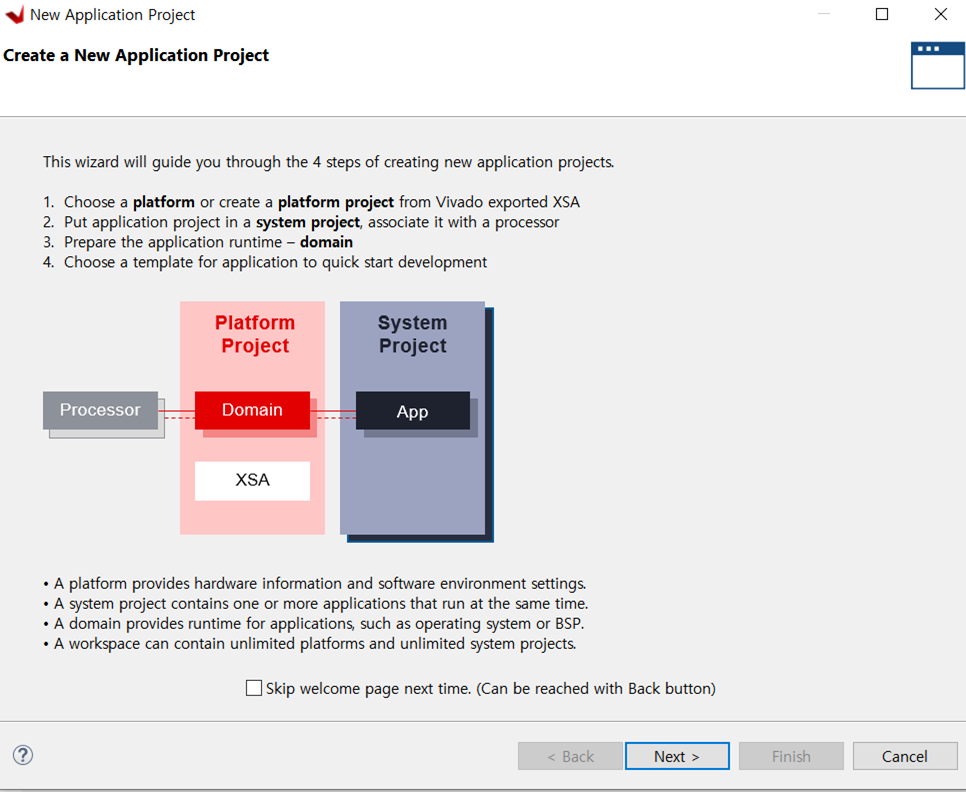

Next

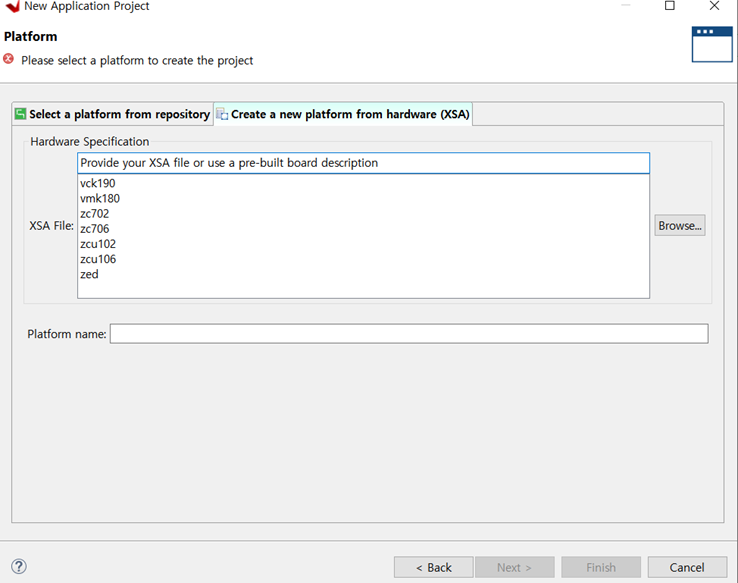

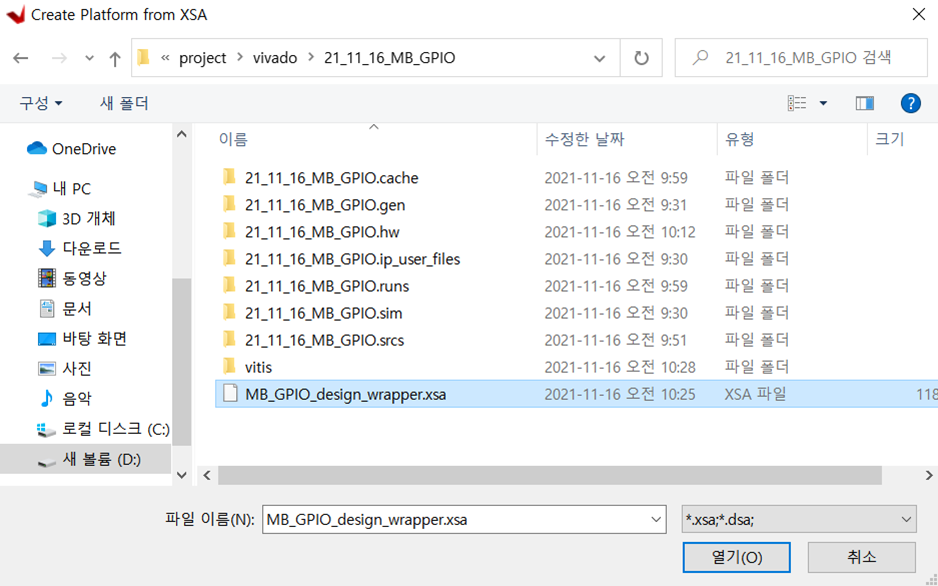

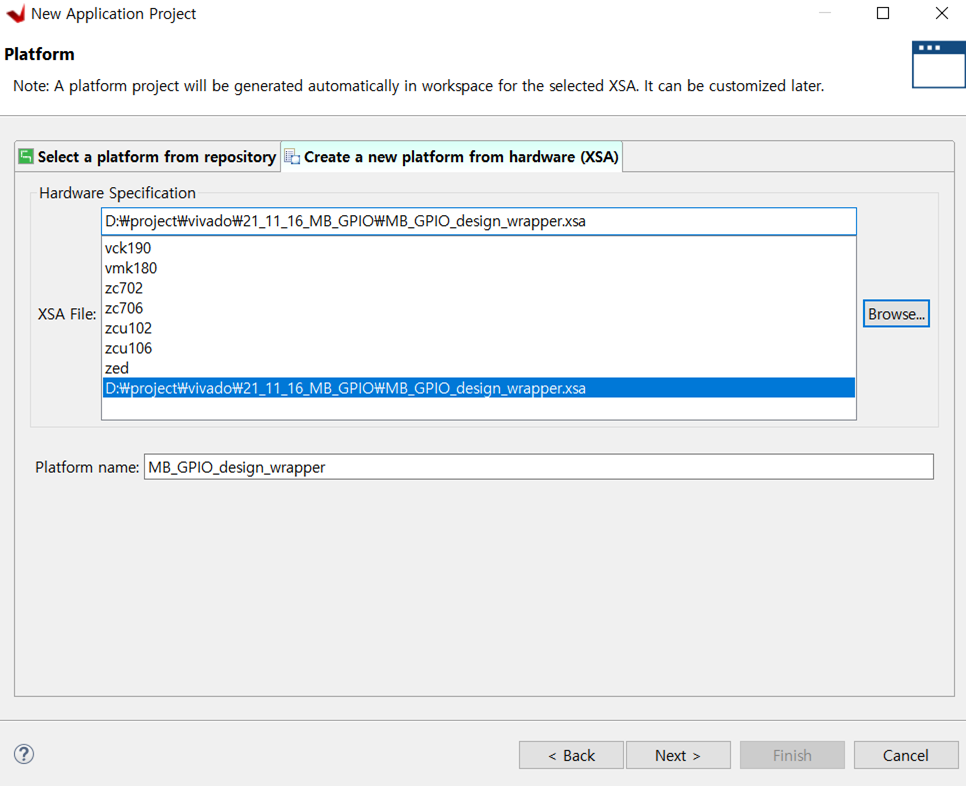

다음 창으로 넘어와서는 상단 바의 우측 Create a new platform from hardware(XSA)를 누르고

우측의 Browse...을 누른다

좀전에 저장 해두었던 .xsa파일을 불러온다

Next

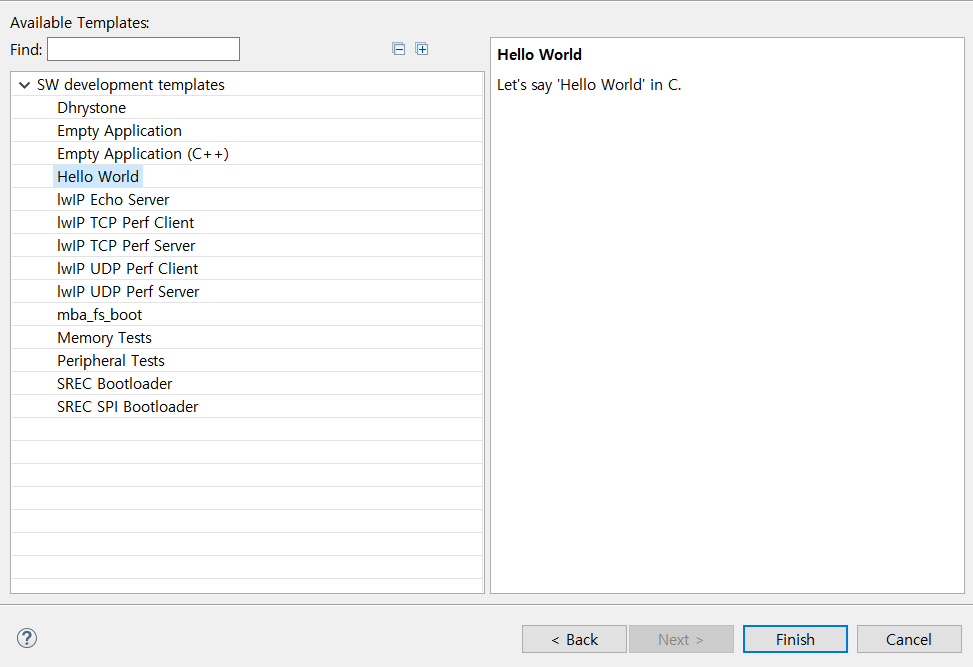

Hello World 를 누른뒤 Finish를 누른다

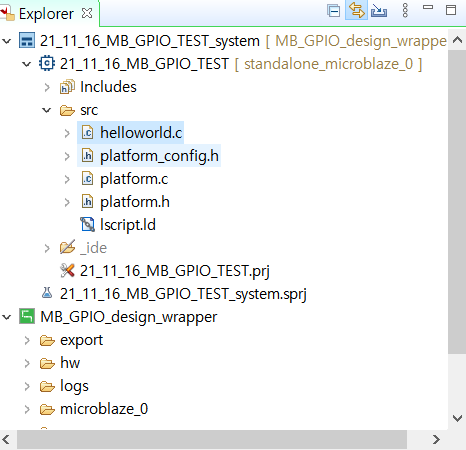

그러면 기본적인 스크립트가 짜여있는 창이 나온다

helloworld.c가 avr의 main 이라고 생각하면 된다

안쪽에 코딩을 하고 나면

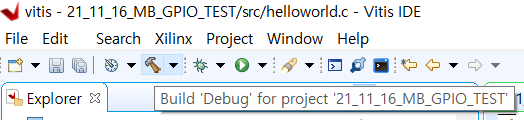

망치 모양을 눌러서 컴파일이 가능하다

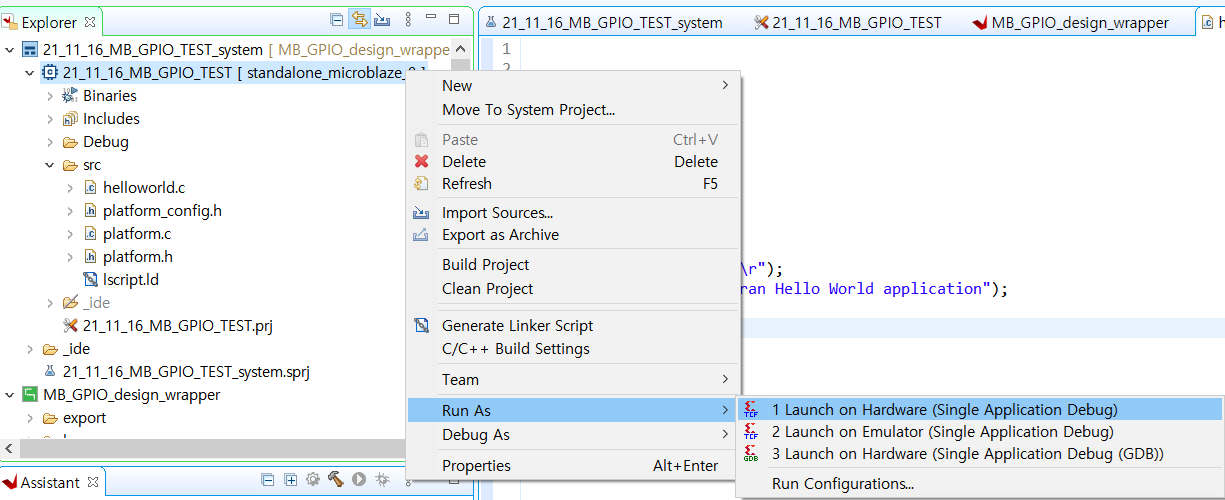

컴파일을 하고 난뒤에 내가 사용하는 칩을 우클릭 -> Run As -> 1번을 선택

이러면 기본적인것은 다한것이다.

vitis는 주석을 한국어로 달경우에 글자가 깨지기 때문에 이를 방지하기 위해서 설정을 해줘야 한다.

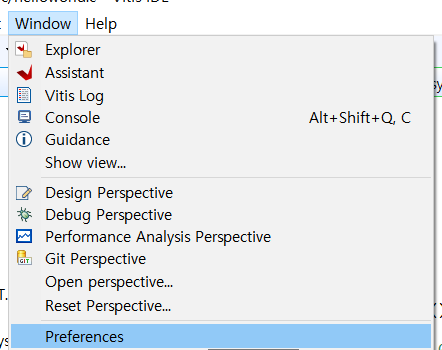

Window 에서 Preferences 를 선택

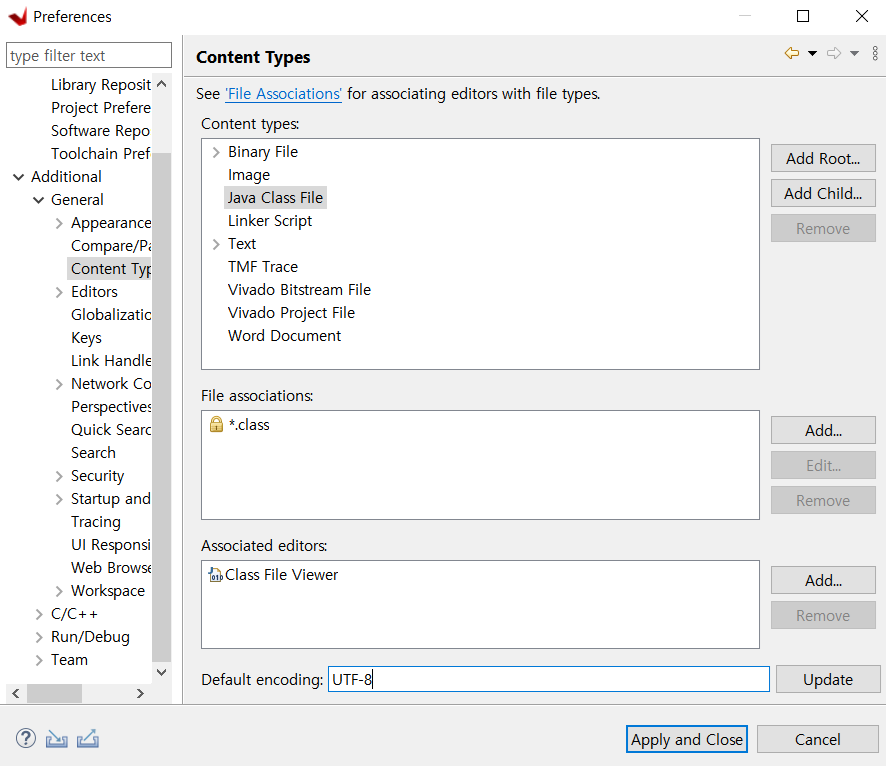

왼쪽 창에서 Additional -> General -> Content Type -> 우측창에서 Java Class File -> Default encoding 에 UTF-8을

을 적은뒤에 Update 를 클릭

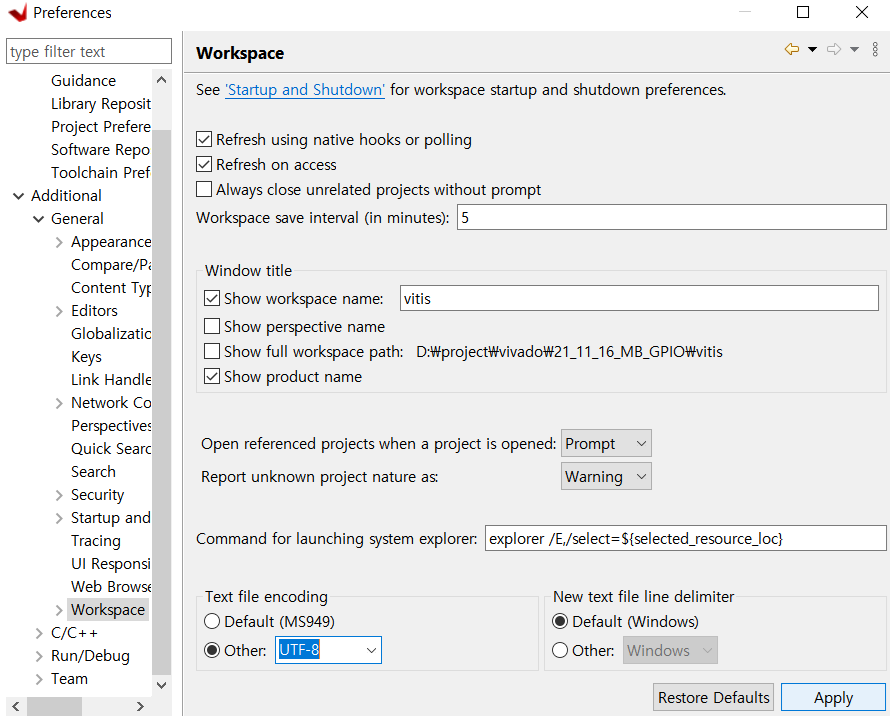

General -> Workspace -> 하단부의 Othe 에서 UTF-8을 선택한뒤 Apply클릭

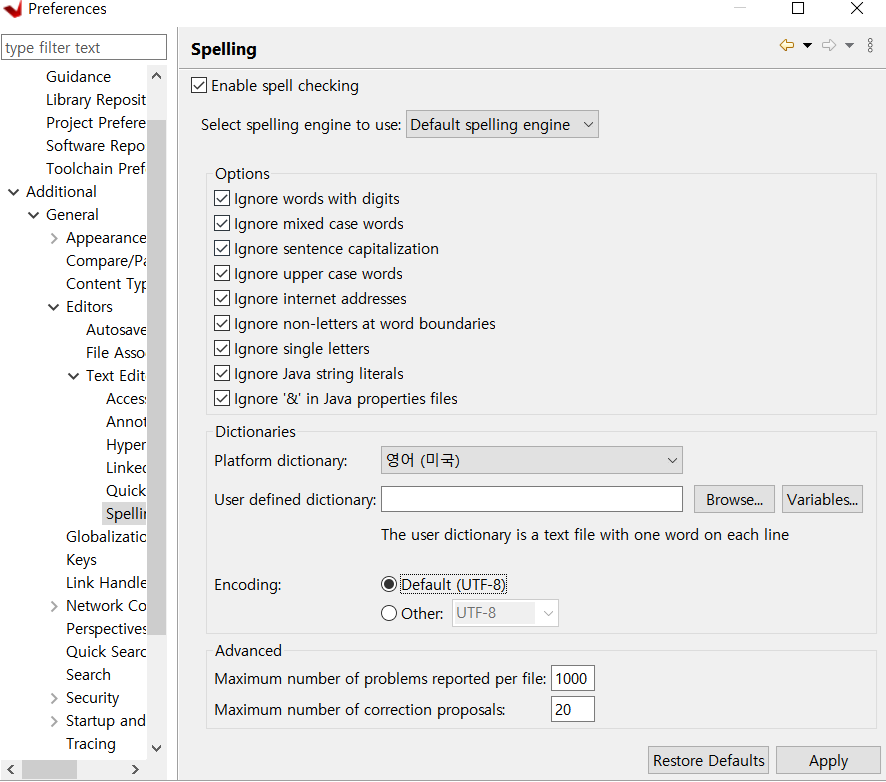

General –> editors –> text editors -> Spelling –> 우측 Encoding쪽에 Default UTF-8 선택 -> apply클릭

이렇게 하면 설정이 완료 되었다 한글을 사용하여도 글자가 깨지지 않을것이다.

'코딩 > FPGA' 카테고리의 다른 글

| [FPGA] 세탁기 프로젝트 (0) | 2021.11.30 |

|---|---|

| [FPGA] FPGA+ AVR Buzzer + Motor (0) | 2021.11.12 |

| [FPGA] FPGA + AVR StopWatch (0) | 2021.11.12 |

| FPGA IP PACKAGE 하는 방법 (0) | 2021.11.12 |

| [FPGA] Stopwatch + Clock + LED bar (0) | 2021.11.10 |